模拟CMOS集成电路设计学习笔记(一) 集成电路设计导论

集成电路设计是现代电子工业的基石,而模拟CMOS集成电路设计则是连接现实物理世界与数字处理系统的关键桥梁。本系列笔记旨在系统梳理模拟CMOS集成电路设计的核心知识与实践要点,首篇将聚焦于集成电路设计的宏观背景、基本流程与模拟设计的独特地位。

一、集成电路设计的宏观图景

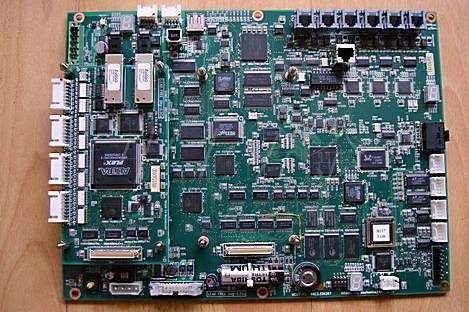

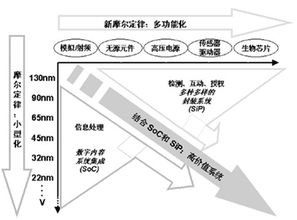

集成电路设计并非孤立的技术环节,而是深深植根于半导体工艺、电路理论、系统架构与应用需求的交叉领域。其发展始终遵循“摩尔定律”的指引,朝着更高集成度、更低功耗、更高性能的方向演进。从设计层次上看,可分为系统级、架构级、电路级和物理级设计。模拟CMOS设计主要活跃在电路级与物理级,负责将连续的物理信号(如声音、温度、光强)转换为可被数字系统处理的电信号,或将数字信号还原为模拟输出。

二、集成电路设计的基本流程

一个典型的集成电路设计流程是一个多次迭代、层层细化的过程:

- 需求分析与规格制定:明确芯片的功能、性能指标(如速度、精度、功耗、面积)、工作环境及工艺要求。

- 架构设计与模块划分:根据规格,进行系统架构设计,并将复杂功能划分为可管理的功能模块(如放大器、滤波器、振荡器、数据转换器等)。

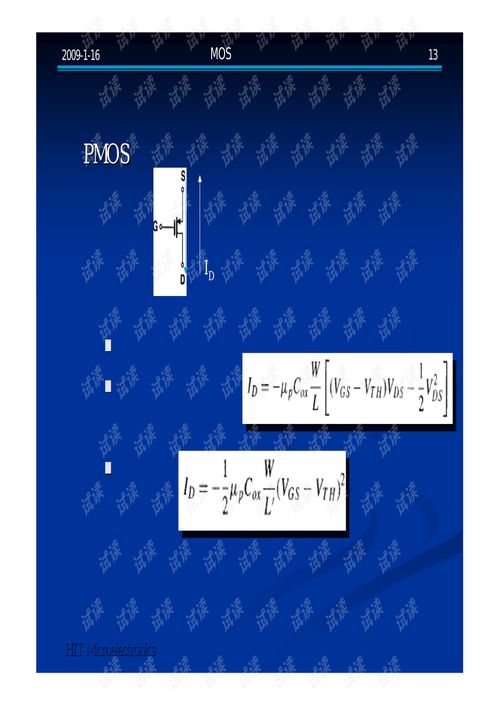

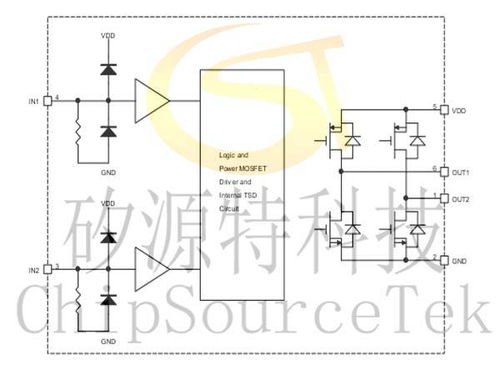

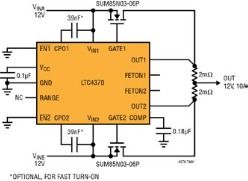

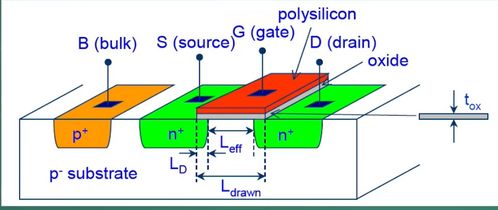

- 电路设计与仿真:此为模拟设计的核心。设计师使用晶体管级电路图,利用CMOS工艺库中的器件模型(如NMOS、PMOS),搭建具体电路,并通过SPICE等仿真工具进行直流、交流、瞬态及噪声等分析,以验证电路功能与性能是否达标。

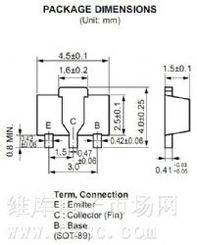

- 版图设计:将经过验证的电路图转化为符合特定工艺规则的几何图形(版图)。模拟版图设计极具挑战性,需精心考虑器件匹配、噪声隔离、寄生效应、电流密度、可靠性(如天线效应、闩锁效应)等诸多因素。

- 物理验证与后仿真:对完成的版图进行设计规则检查、电气规则检查以及版图与电路图一致性检查。提取版图的寄生参数(电阻、电容),进行包含寄生效应的后仿真,这是确保芯片最终性能与设计一致的关键步骤。

- 流片与测试:将最终版图数据提交给晶圆厂制造(流片),成品芯片返回后进行严格的测试,验证其实际性能。

三、模拟CMOS设计的独特挑战与价值

在数字电路占据主流的今天,模拟设计依然不可或缺,因为现实世界本质上是模拟的。模拟CMOS设计面临诸多独特挑战:

- 设计复杂性高:性能受工艺偏差、温度变化、电源噪声、寄生效应影响巨大,需要设计师具备深厚的器件物理、电路理论和直觉经验。

- 自动化程度相对较低:相比于数字电路的高度自动化综合与布局布线,模拟电路设计仍严重依赖设计师的手工优化与经验判断。

- 验证维度多:需要验证直流工作点、增益、带宽、噪声、线性度、电源抑制比、温度稳定性等多个性能指标。

其核心价值在于处理接口信号、提供精确的参考源、实现高效的电源管理以及完成高保真的信号链处理。掌握模拟CMOS集成电路设计,意味着掌握了连接物理世界与数字世界的钥匙,是高端芯片设计能力的重要标志。

在后续的学习笔记中,我们将深入CMOS器件物理、单级放大器、差分结构、频率响应、噪声、反馈、运算放大器、数据转换器等具体专题,逐步构建完整的模拟CMOS集成电路设计知识体系。

如若转载,请注明出处:http://www.zctsny.com/product/14.html

更新时间:2026-04-16 06:21:31